2023-09-14 06:53:17 发布人:hao333 阅读( 4646)

要说最近硬件圈最大的一件事就是华为 Mate 60 Pro 突然开售,大家应该没意见吧?在突然开售后, Mate 60 Pro 也像一座金矿一样,被各路媒体老师...

要说最近硬件圈最大的一件事就是华为 Mate 60 Pro 突然开售,大家应该没意见吧?

在突然开售后, Mate 60 Pro 也像一座金矿一样,被各路媒体老师不断挖掘。

之前托尼也蹭上了这台手机的热度,在拿到实机的第一时间跟大家分享了上手体验。

不过,托尼觉得只有上手体验这还不够,因为关于大家最关心的 5G 麒麟芯片,我还没有给大家讲清楚。

但当托尼和硬件部小伙伴们策划这个选题的时候,发现关于 Mate60 Pro 以及麒麟 9000S 的信息基本上已经被同行们给讲完了。

可恶。。。终究还是手慢了。

为了不跟同行们重复讲一样的东西,我们稍微换了个思路——绕开了处理器本身,看看华为在 “ 造芯片 ” 这块还有没有什么料可以挖。

结果发现还真有!

实际上,这个东西并不是托尼先看到的,而是一位名叫 “ 问题先生 ” 的博主先看到的。

问题先生在业内还是很知名的,据说有 20 多年的半导体相关从业经验。

两个多月前,他发了一个视频,分析了华为刚刚解禁的一项半导体晶体管制备专利。

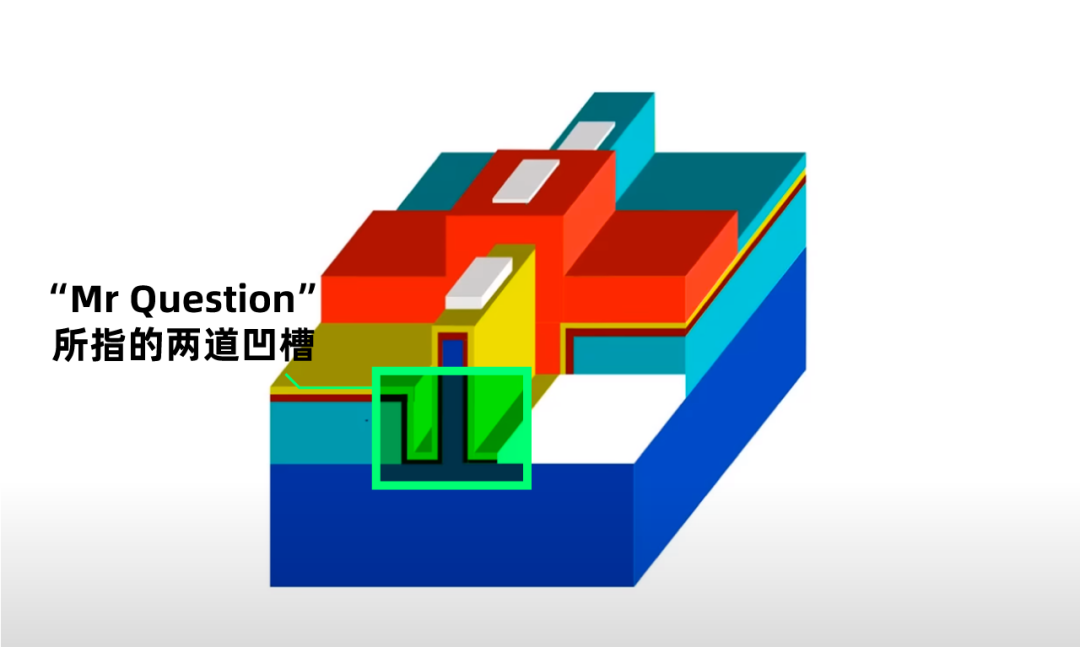

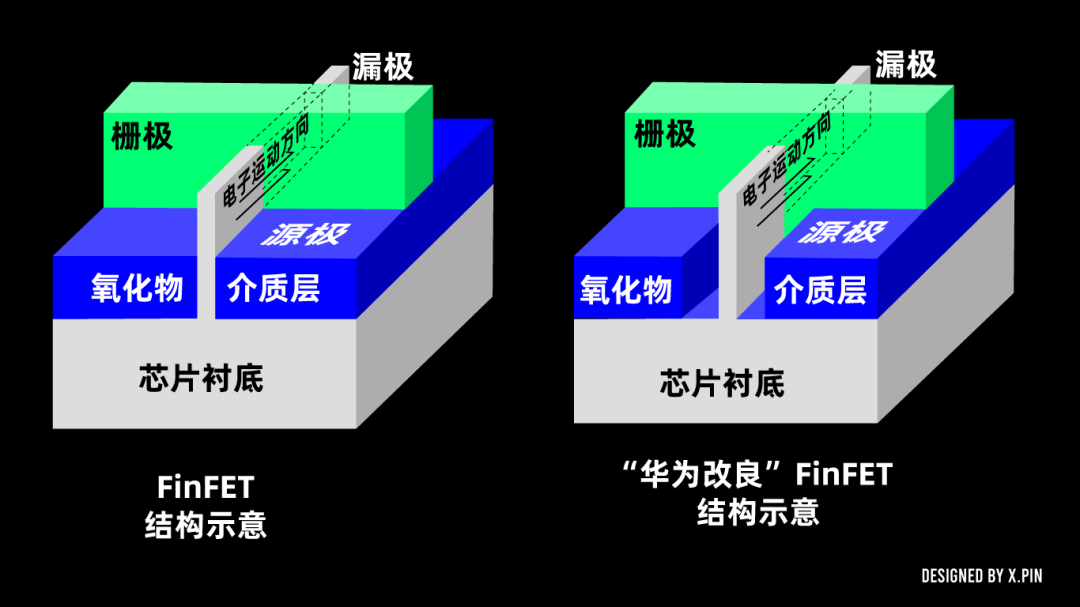

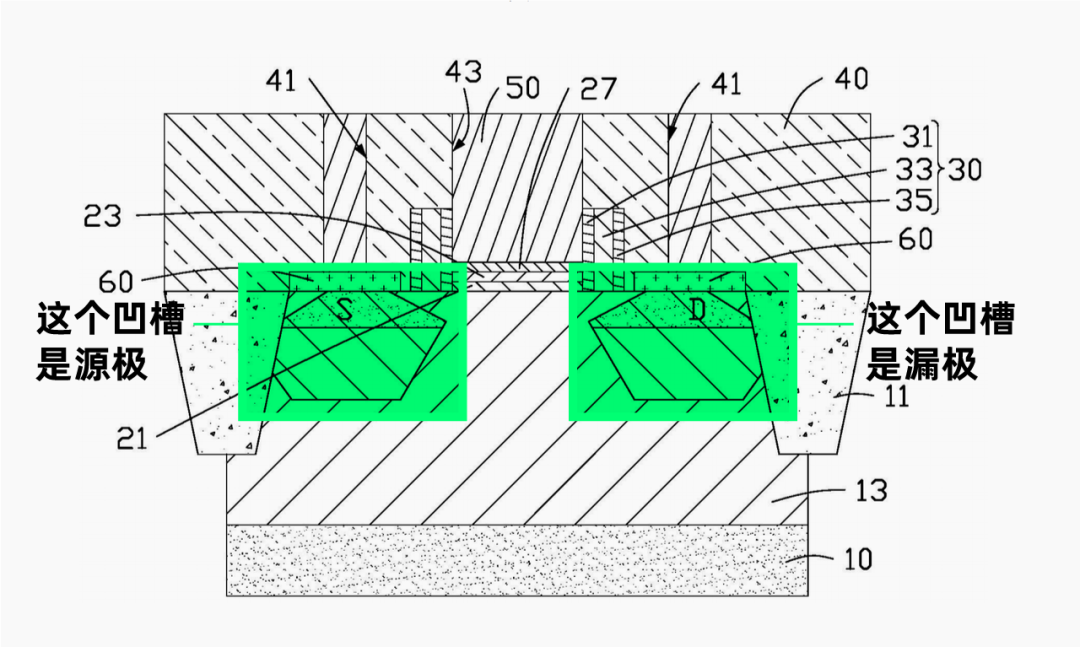

他根据专利的文字描述推测,华为打算在传统 FinFET 的基础上挖两道凹槽,通过改良 FinFET 的结构,提升了晶体管漏电的控制能力。

进而降低了功耗,改善了性能。

问题先生预估:在同制程下, “ 华为 FinFET” 的能效比传统 FinFET 提升 20% ,可以把7nm 工艺发挥出 5nm 的性能;5nm 制程做成3nm 的能效。

海外企业们大开大合,刚搞完 5nm 就想搞 3nm 。华为则是未雨绸缪,考虑着怎么能从上一代制程上挤出更多的水分。

而且 7nm 工艺的极限好像真的被华为这个专利探索出来了不少,真就是______。

但。。。职业习惯让我多做了一步操作,我试着去搜了下问题先生提到的华为专利,结果发现问题先生猜错了。

是这样的,问题先生之所以会猜错,是因为他只看到了专利前面部分的文字描述,然后根据专利的文字描述自己画了一张结构图。

但这个自制的结构图和华为官方的专利配图差的还是有点儿远,所以才误解了华为设计两道凹槽的实际作用。

等到我们再去知识产权局的数据库里查资料的时候,华为已经把对应的专利配图给补上了。

通过看华为自己提供的图片,我们才发现了这两道凹槽的真正作用。

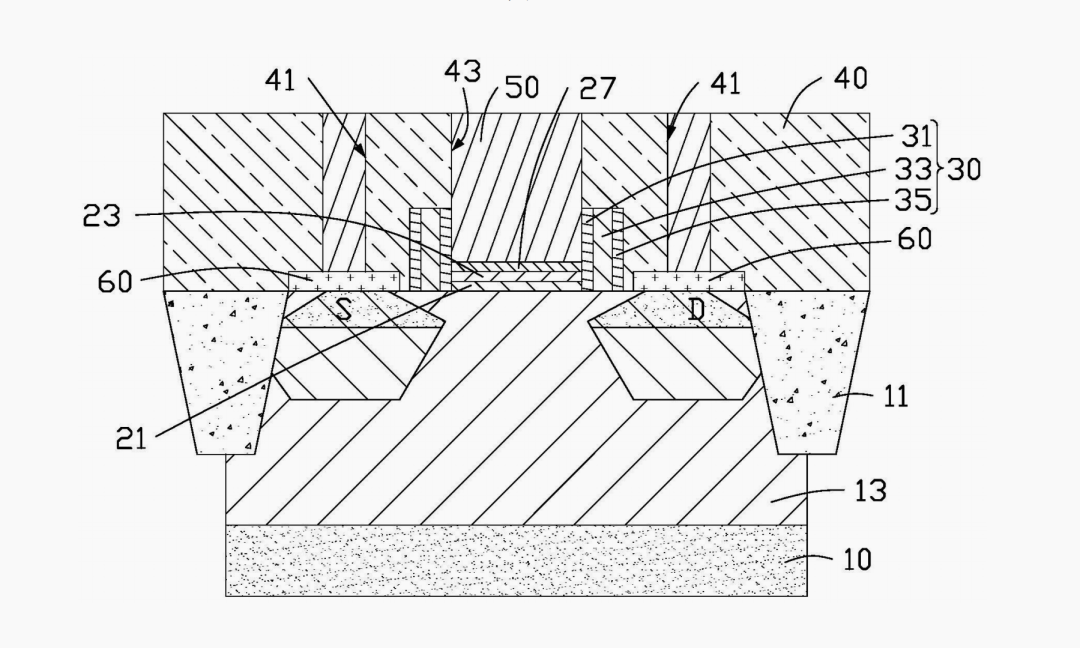

简单来说,华为专利里提到的两道凹槽实际上是用来分别形成源极跟漏极的,这个源极跟漏极相当于开关的两端,当开关闭合时,电流会从源极入,从漏极出。

那么这个专利真正讲的东西是什么呢?

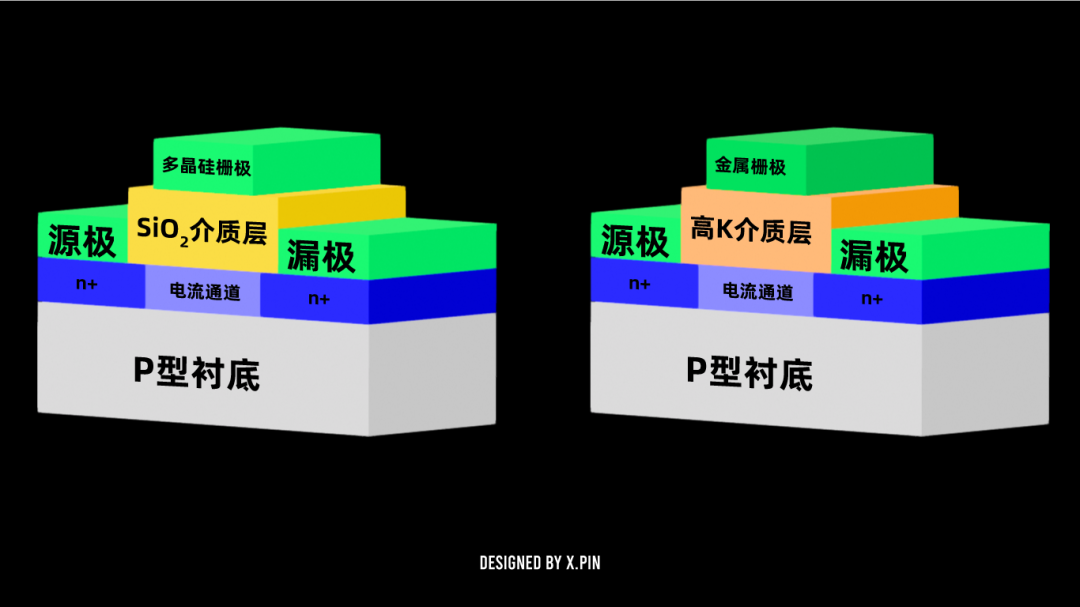

它讲的是华为研发出了一种晶体管制作的改良工艺,通过这个改良工艺,可以让制作高介电常数金属栅极的制作步骤减少。

这个高介电常数金属栅极技术是28nm 制程节点后的必备技术,但以往的制作工艺复杂,导致它比发展更早、性能更差的多晶硅栅极 技术,要多出几个工艺步骤,这样会造成生产周期延长以及成本增加的问题。

在专利中,华为讲到,改良后的工艺可以节省至少 3 个主要工艺步骤,以及若干个次要工艺步骤。

从理论来说,这样可以降低整体的生产难度,提升不少良率,进而大幅降低成本,华为的初步预估是每片晶圆至少可以节省 20 美金。

按照之前 Mate 系列出货量以百万计的情况来看,假如华为真的要开始自己造芯片了,那么实装这项专利,就能给华为省下一笔相当可观的成本。

同行们想要借鉴还得给华为交专利费。

赢麻了。。。_______!

嗯。。。不过,虽然节省成本的专利也很棒,可它并不是大家原本猜测的那样,把 “7nm” 当 “5nm” 耍的炸裂技术。

把实际情况和我们的心理预期做对比,就显得这个专利好像也并没有那么厉害了。

所以本来我们稍微有点儿心灰意冷,打算跟大家稍微解释一下这个小小的专利乌龙就结束了。

不过就在托尼找资料的过程中还发现,华为这次放出来的专利不是一个,而是一批!

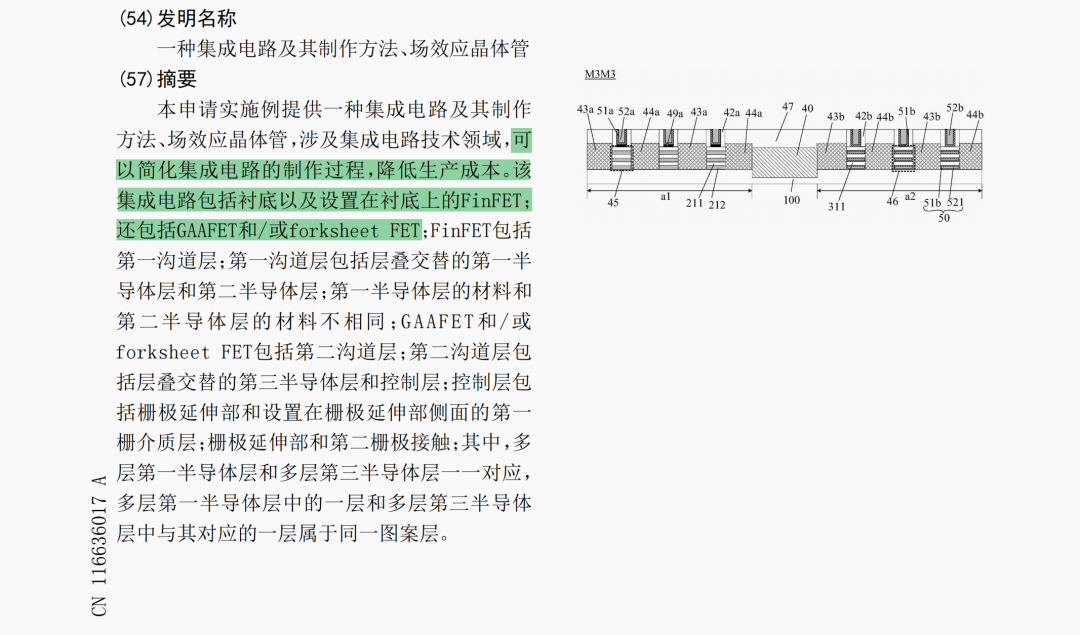

其中另外一个编号 CN116636017A 的发明专利,看起来相当有意思。

不卖关子,在这项专利的文档中,华为直接把FinFET ,和GAAFET 或Forksheet FET ,做进一个集成电路里。

并且简化了电路的制作步骤!

这里可能会有小伙伴要问了:这个突然冒出来的 GAAFET 和 Forksheet FET 又是啥呢?

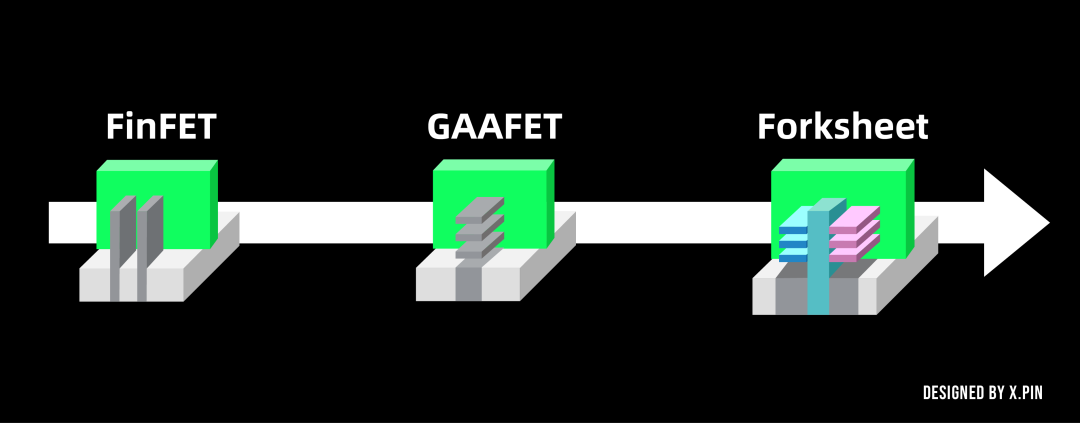

无论是咱们前面讲到的 FinFET ,还是这个 GAAFET 和 Forksheet FET ,它们都是晶体管的一种结构类型。

相比 FinFET,GAAFET 和 Forksheet FET 的漏电控制性能更强。

其中 FinFET 是目前芯片制造中的主流方案,而 GAAFET 和 Forksheet FET 还未实现量产,但是因为 3nm 之后的工艺更难控制 FinFET 的漏电,所以未来一定是属于 GAA 和 Forksheet 的。

诶不过。。。既然 GAAFET 和 Forksheet FET 更先进,为啥华为还要把它们跟 FinFET 做进一个集成电路里呢?

全用 GAAFET 或者 Forksheet FET 不就得了?

emmmmm ,是这样的。

一方面是因为 FinFET 跟 GAAFET 都有自己的优缺点。

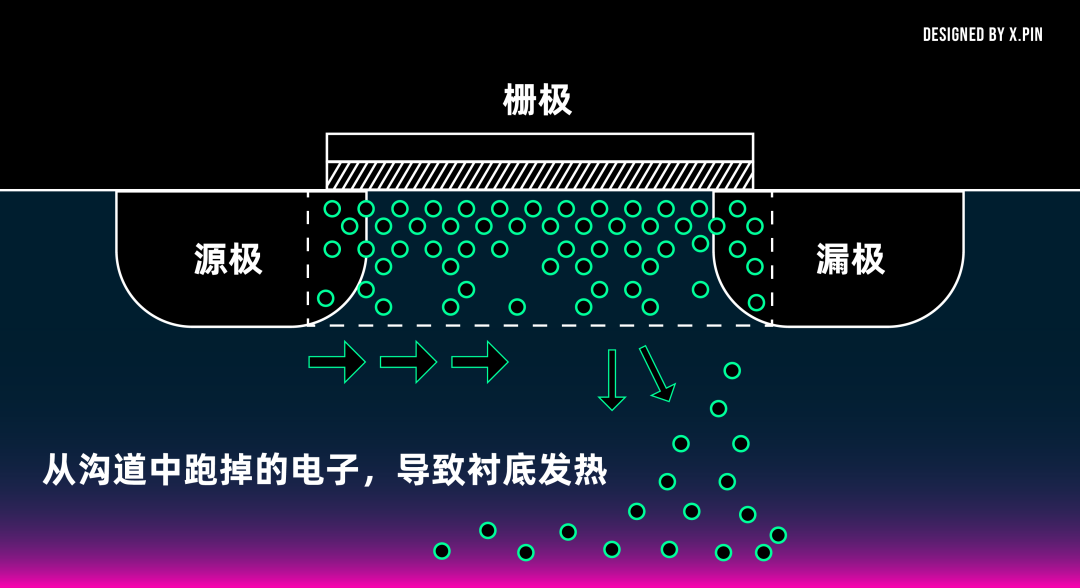

像 FinFET ,它随着制程工艺的升级,尺寸的缩小,会出现漏电流控制性能变差的问题。

这给大家提一嘴漏电流是怎么回事:实际上,电流并不是百分之百从晶体管的源极流向漏极的,这期间有些不受控制的电子会溜掉,这样一来就会产生漏电,而漏的电流越多,会导致功耗和发热越严重。

而 GAAFET/ Forksheet FET ,这类结构在尺寸缩小后,依旧可以保留出色的漏电流控制表现,所以很适合用在 5nm 制程节点之后的芯片上。

但 GAAFET/ Forksheet FET 也有一个缺点,那就是它的电阻会比 FinFET 更大。

所以即使是 3nm 的集成电路里,也不能一味只用 GAA 或者 Forksheet ,也还是需要根据实际情况搭配 FinFET 进行设计。

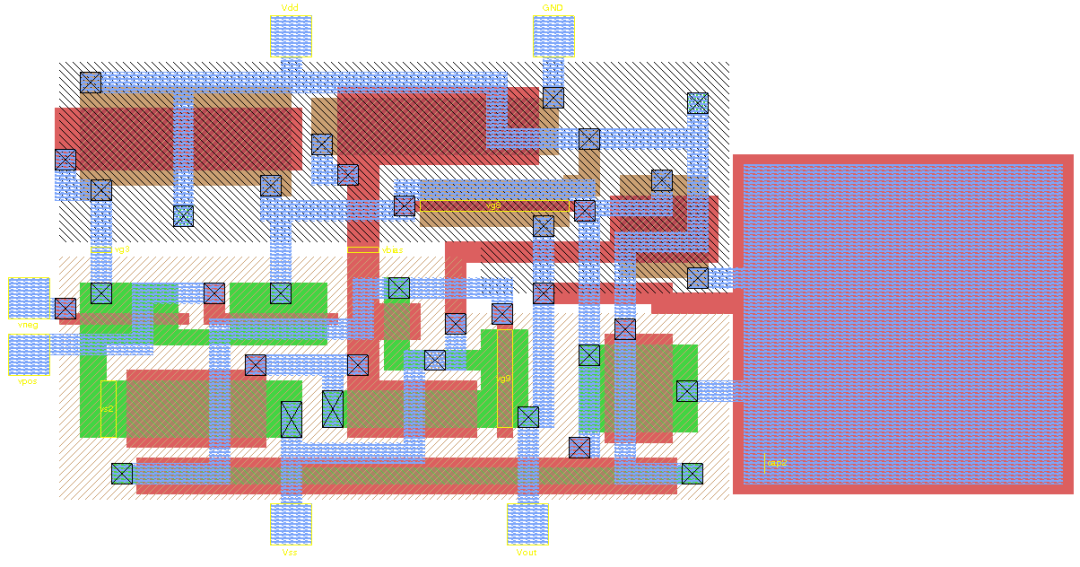

一个简单的 CMOS 放大版集成电路版图

比如:芯片里的逻辑电路,它是负责运算的,在运算时电路中的晶体管们会进行频繁的开和关,这样就对晶体管的漏电流表现有更高的要求。

同时为了算得更快,晶体管的数量自然也是越多越好。

所以,逻辑电路需要那种在尺寸缩小后,依旧可以有出色的漏电流控制表现的晶体管,那自然就是 GAAFET 或 Forksheet FET 了。

但是像需要处理连续信息的信号的模拟电路,以及有高电压需求的输入输出电路,它们需要电阻更小的通道,自然就是用 FinFET 更合适。

看到这大家应该就明白了,华为的做法相当于:我在一个集成电路中,根据需求来设计 FinFET 和 GAAFET 或 Forksheet FET ,比如输入输出电路、模拟信号处理电路用 FinFET ,逻辑电路用 GAAFET 或 Forksheet FET ,存储电路可以任意选择一种。

这样一来,就可以最大程度地发挥不同晶体管结构的性能。

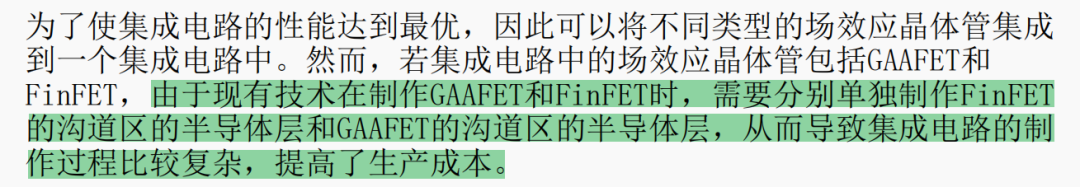

不过,要做到这件事儿并不容易。

因为在现有的技术条件下,我们要在一个集成电路里制作 FinFET 和 GAAFET/ Forksheet FET ,需要分别单独制作它们各自沟道区内的半导体层,比如:先做好了FinFET,再去做GAAFET。

这步骤一分开,制作过程就变得非常繁琐,生产成本也会随之升高。

这里就要讲到华为这项专利的精髓部分了,他们为了减少制作步骤,在开始制造前的版图阶段会先对芯片的图案层进行标记,比如第一半导体层、第二半导体层、第三半导体层、第四半导体层。

说实话,托尼一开始也有点搞不明白这个 “ 第一第二。。。” 到底在讲啥,直到把 28 页的文档 “ 啃 ” 下来后,才大概理解了其中的奥妙。

这个第一、第二。。。不是用来表示先后和重要性,而是为了标记不同的图案层,打个不太恰当的比方:FinFET 的第一半导体层对应了GAAFET的第三半导体层。

不严谨地说,这么一对应,就能让它们被同时制作。

利用这个方法,华为就可以不用像前面讲的那样——“先做这个再做那个”,这样就大幅简化了电路的制作过程,减少工期和成本。

妙啊 ~ 如果这项专利在未来可以落地,那么对于华为的芯片竞争是很有利的——当然了,只是假如、假如华为真的想自己做芯片的话。

毕竟专利本身只是个技术储备,大家不要听风就是雨,要理智判断。

而且虽然咱们短短几句话就讲完了华为的巧思,但实际操作起来还是困难重重的。

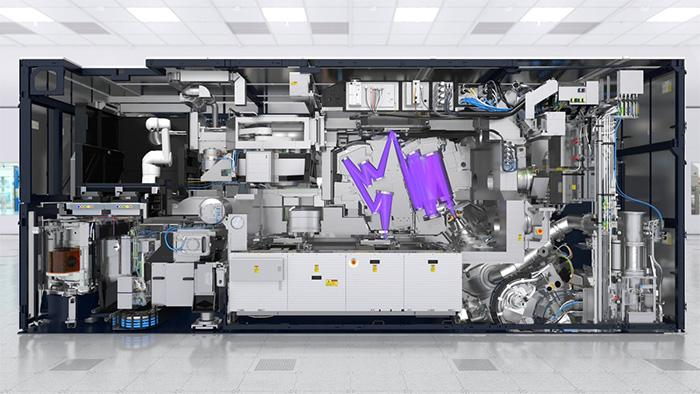

因为 GAAFET 、 Forksheet FET 的结构又小又复杂,不仅对蚀刻工艺的要求非常高,而且还要用到 EUV 光刻机,这个东西现阶段国内很难搞定。。。

而且托尼还问了一下搞半导体设计的朋友,发现除了咱们前面提的这些内部的光刻问题,外部的电压调控也是需要攻克的。

毕竟两种晶体管结构的特性不同,驱动电压也不同,驱动电路的设计也需要做额外的调整。

看来,华为的这项专利想要真正落地,需要克服很多我们难以想象的困难。

今天我们聊的这些东西,都是华为公开的设计专利,虽然看着很厉害,但很大概率还没有应用到实际的生产步骤上。

因为光有想法不行,还是有很多具体的、配套设备上的问题需要解决的。

不过我发现了一个小细节,不知道有没有小伙伴观察到。

虽然华为这批专利上个月才解禁,但他们真正的提交日期是——2021 年 2 月!

换句话说,两年前,华为就在思考该怎么把芯片造的更好了。

遥遥领先!!!

撰文:粿条 编辑:米罗&结界&大饼

美编:阳光&萱萱&富贵

相关阅读

RelatedReading猜你喜欢

Guessyoulike